### Semi Design Presents...

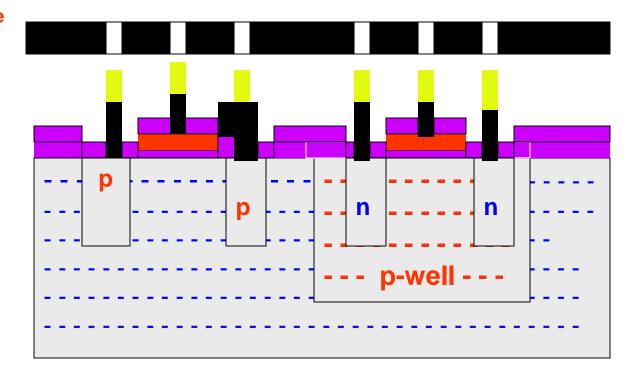

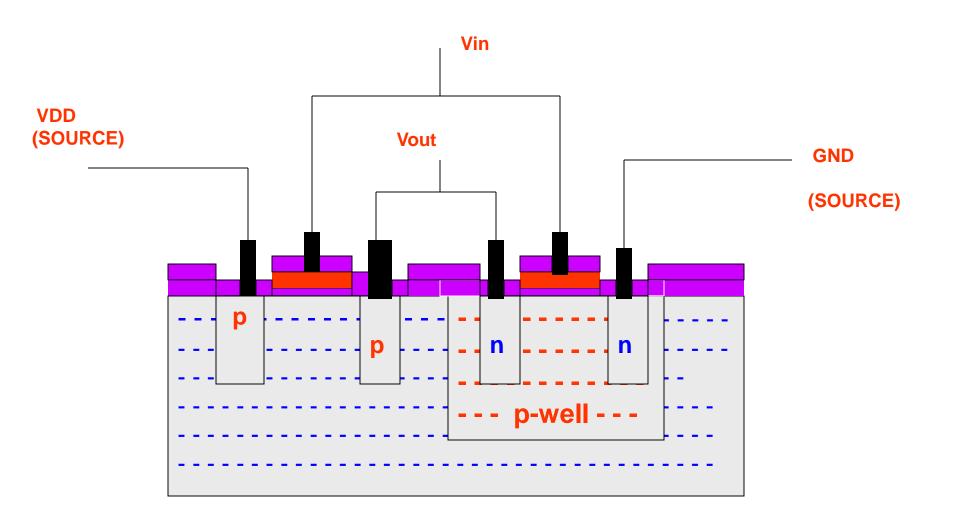

### CMOS Fabrication Process [p-well method]

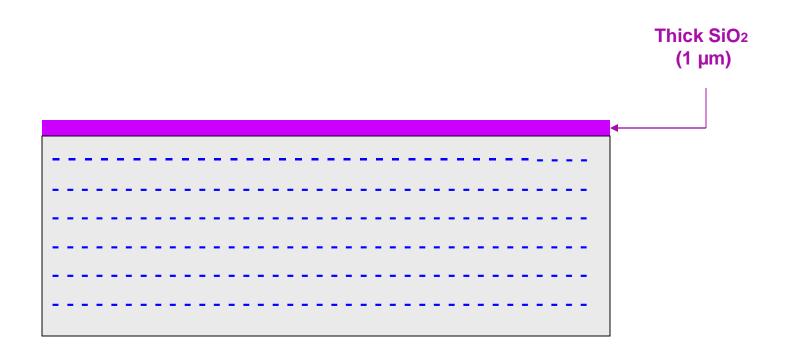

Fig. (1) Pure Si single crystal

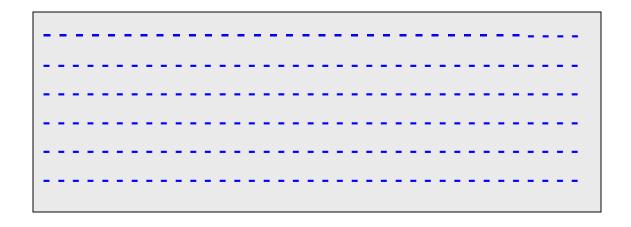

Fig. (2) n-type impurity is lightly doped

Fig. (3) SiO<sub>2</sub> Deposited over si surface

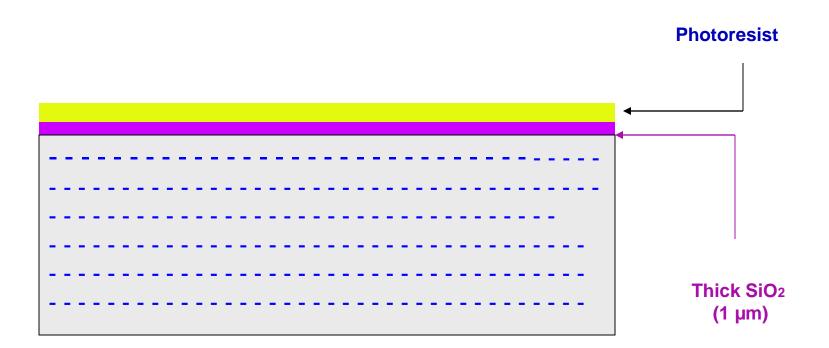

Fig. (4) Photoresist is Deposited over siO2 surface

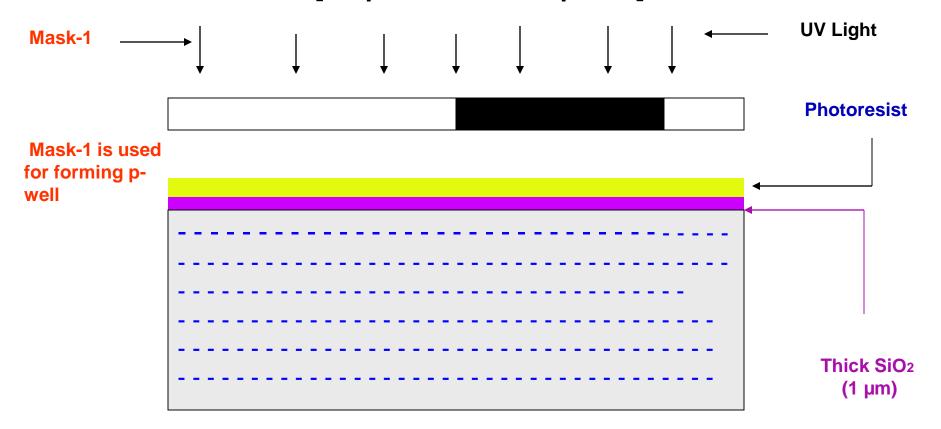

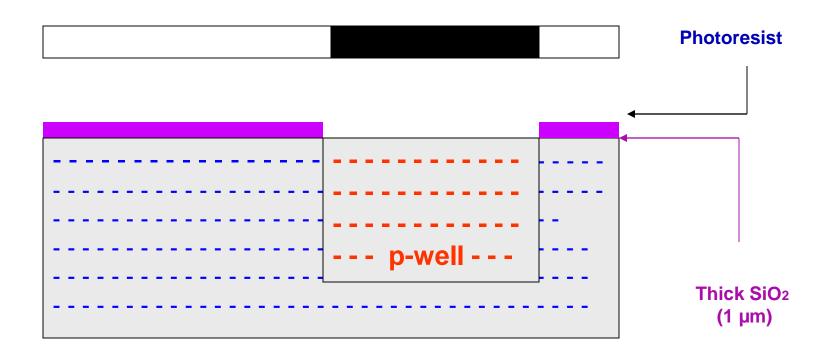

Fig. (5) Photoresist is Deposited over siO2 surface

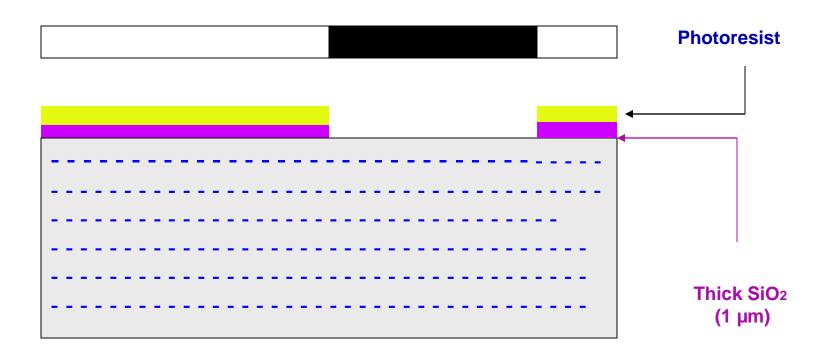

Fig. (6) Photoresist and SiO2 which is not exposed is etched away.

Fig. (7) Hardened Photoresist is stripped away and p-type impurity is added by diffusion process.

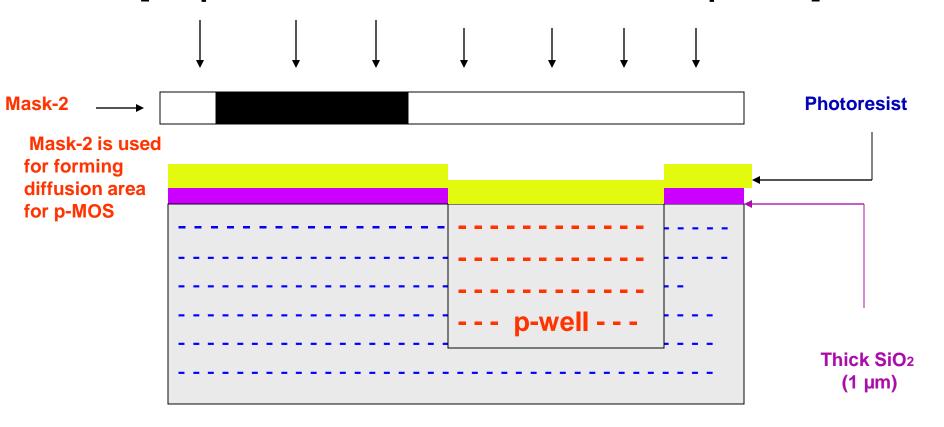

# N-MOS Fabrication Process [Step- formation of Diffusion area for p-MOS]

Fig. (8) Photo resist is grown and exposed in UV Light.

## N-MOS Fabrication Process [Step- formation of Diffusion area for p-MOS]

Fig. (9) Photoresist and SiO<sub>2</sub> which are un-exposed are etched away.

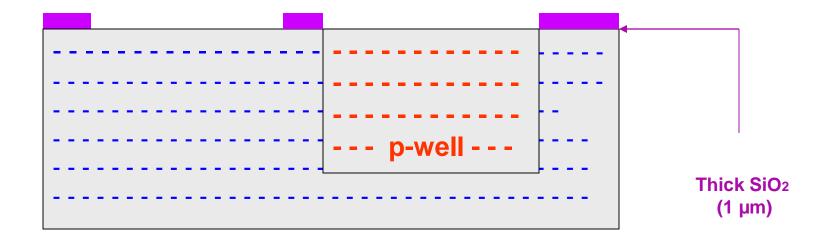

## N-MOS Fabrication Process [Step- formation of Diffusion area for p-MOS]

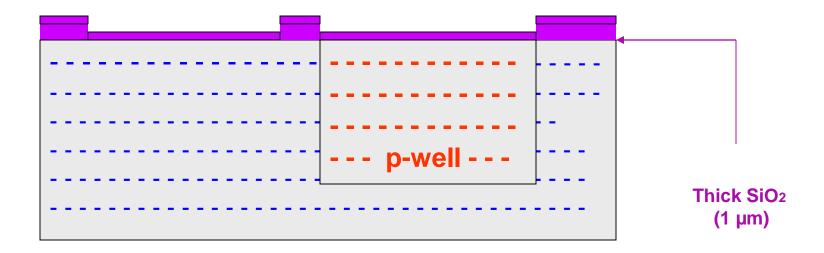

Fig. (10) Polymerised Photoresist is stripped away.

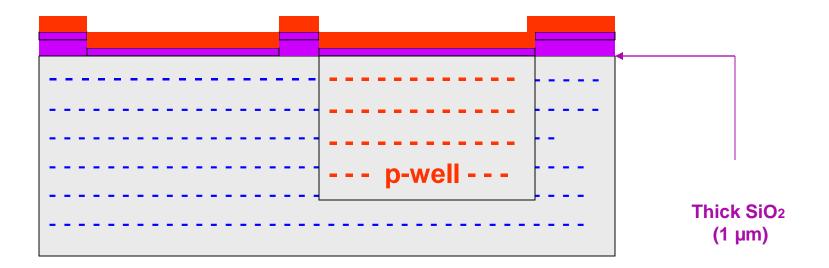

Fig. (11) Deposit Thinox

Fig. (12) Deposit Polysilicon

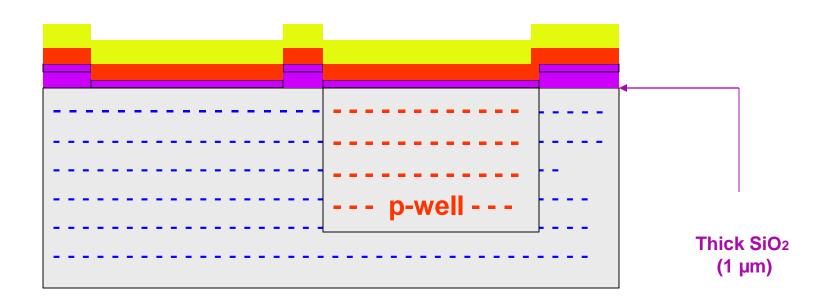

Fig. (13) Deposit Photoresist

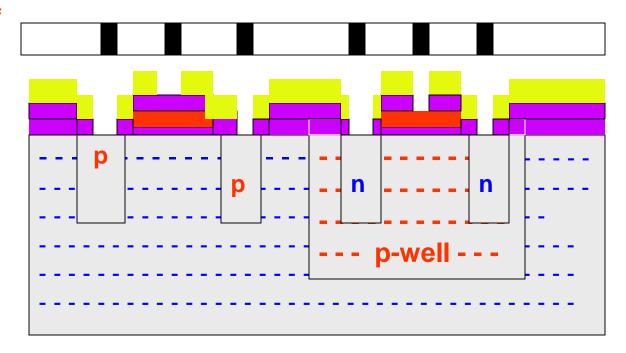

[Step- Gate formation for n-MOS and p-MOS]

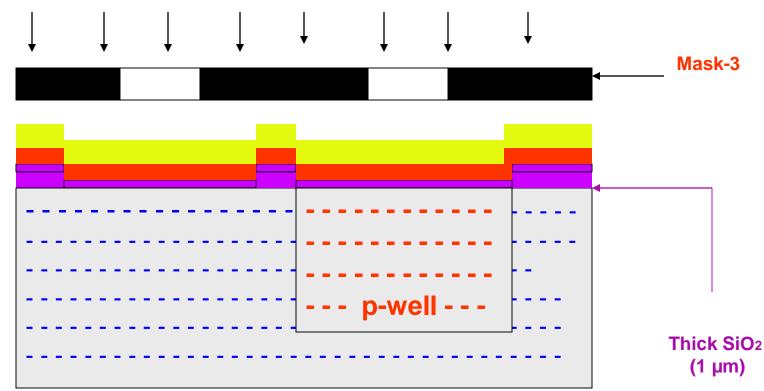

Mask-3 is used for the formation of Two GATEs

Fig. (14) UV Light Exposure to form GATEs of P-MOS and n-MOS

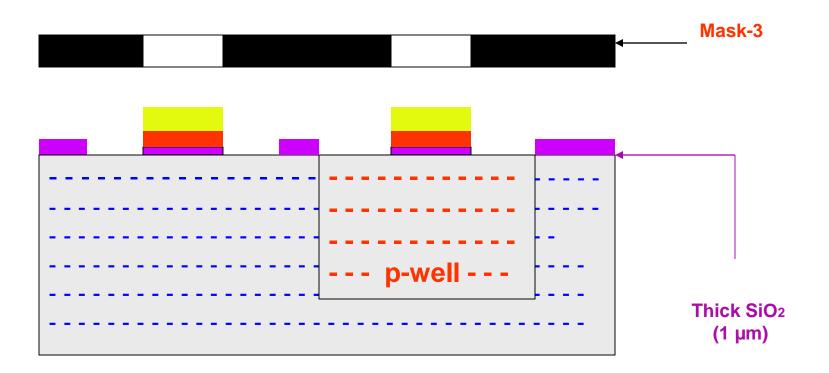

Fig. (15) Un-Exposed Photoresist, Metal and Thinox is etched away.

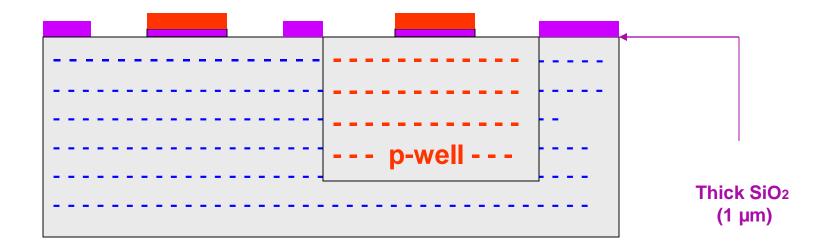

Fig. (16) Polymerised Photoresist is stripped away.

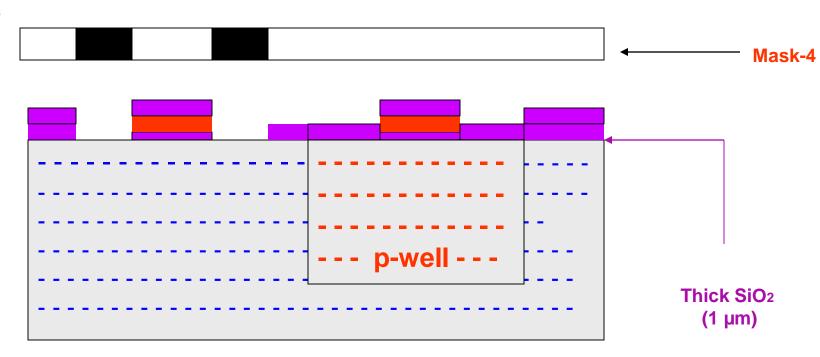

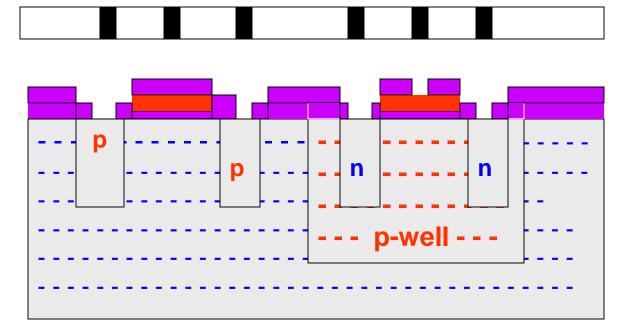

[Step- Source & Drain formation for p-MOS]

Fig. (17) Grow SiO<sub>2</sub> Layer

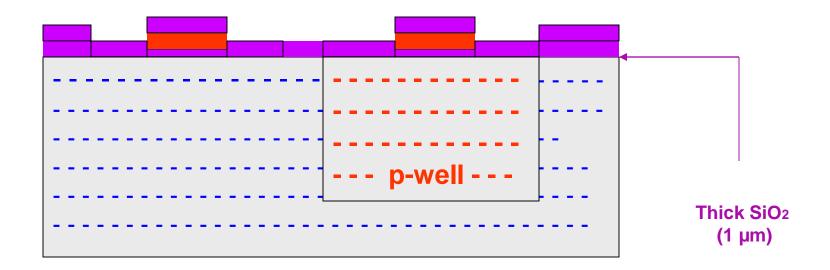

[Step- Source & Drain formation for p-MOS]

Mask-4 is used for the formation of S and D of p-MOS

Fig. (18) Grow Photoresist Layer

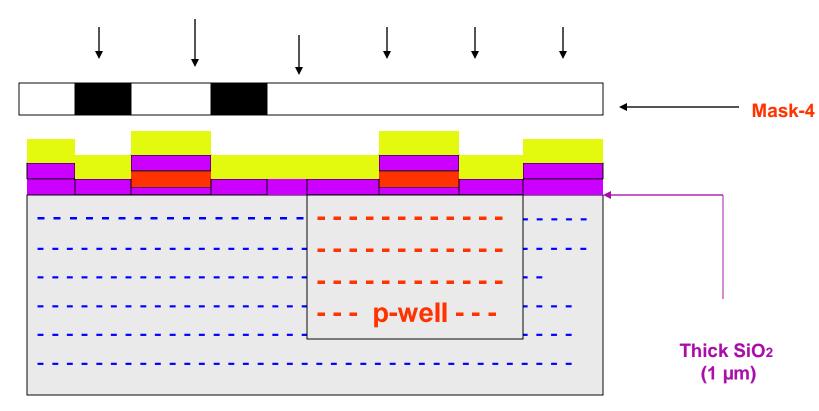

[Step- Source & Drain formation for p-MOS]

Mask-4 is used for the formation of S and D of p-MOS

Fig. (19) Etching of un[polymerised photoresist and SiO<sub>2</sub> below it

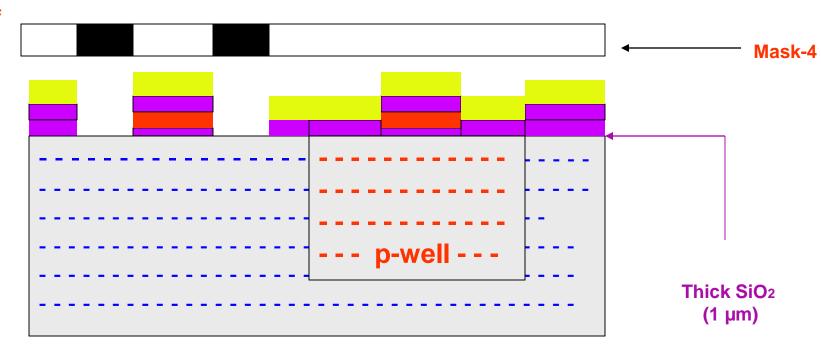

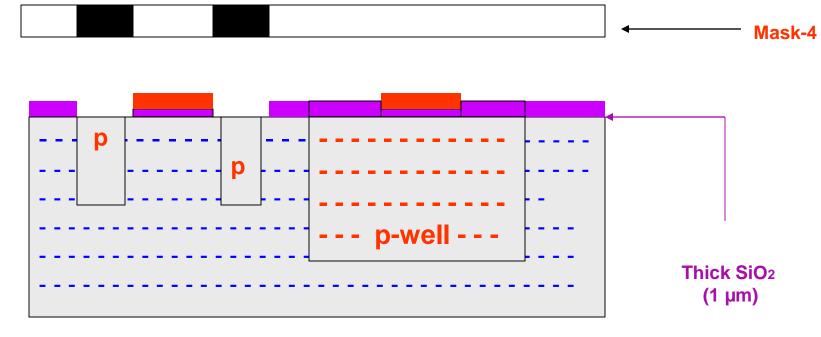

[Step- Source & Drain formation for p-MOS]

Mask-4 is used for the formation of S and D of p-MOS

Fig. (20) Strip away hard photoresist

[Step- Source & Drain formation for p-MOS]

Mask-4 is used for the formation of S and D of p-MOS

Fig. (21) Diffusion of p-type impurity

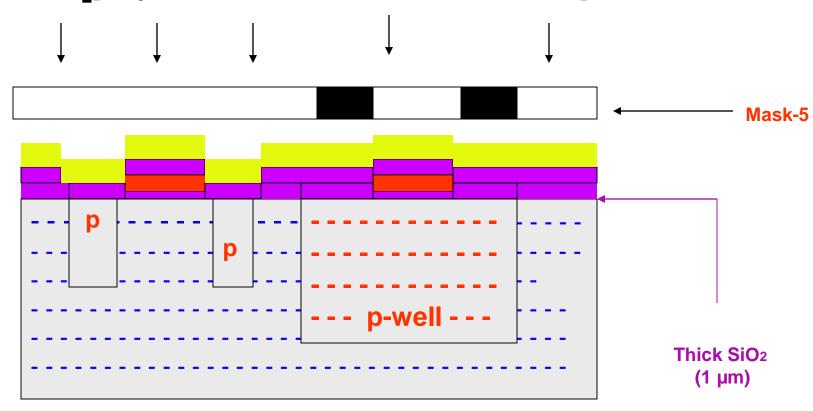

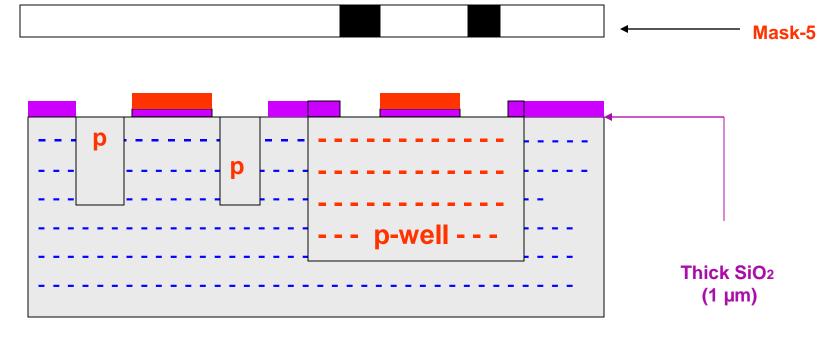

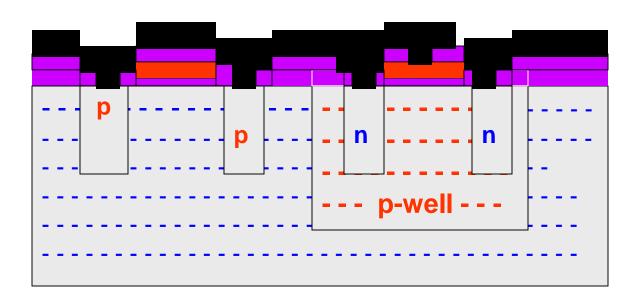

[Step- Source & Drain formation for n-MOS]

Mask-5 is used for the formation of S and D of n-MOS

Fig. (22) Grow photoresist

[Step- Source & Drain formation for n-MOS]

Mask-5 is used for the formation of S and D of n-MOS

Fig. (23) Etching

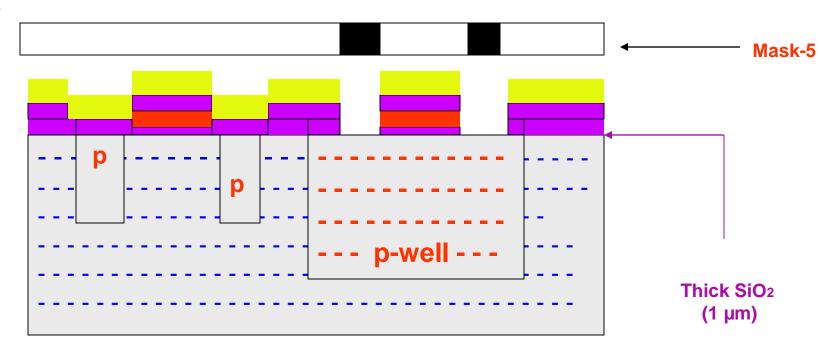

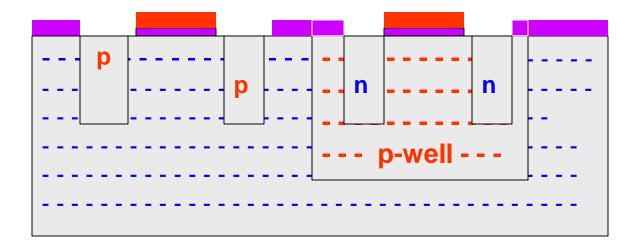

[Step- Source & Drain formation for n-MOS]

Mask-5 is used for the formation of S and D of n-MOS

Fig. (24) Hard photoresist stripped away

[Step- Source & Drain formation for n-MOS]

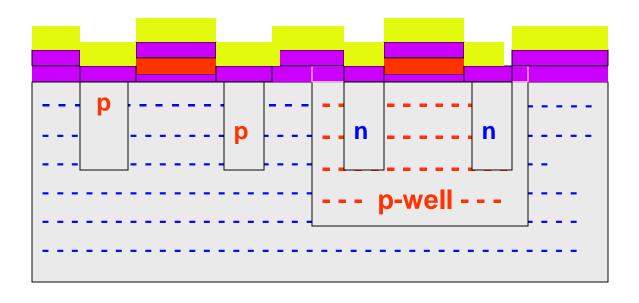

Fig. (25) Diffusion of n-type impurity to form Source and Drain of n-MOS

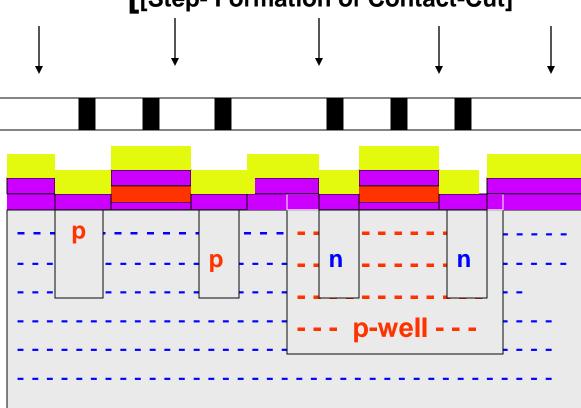

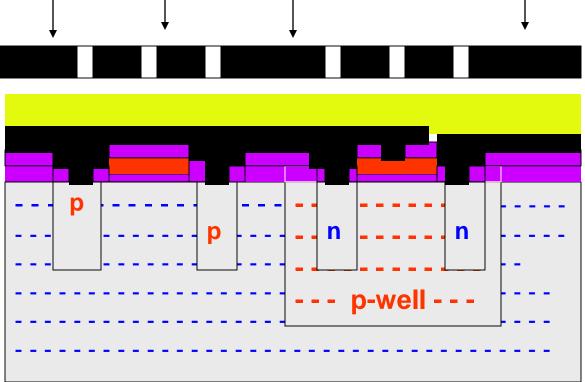

[Step- Formation of Contact-Cut]

[Step- Formation of Contact-Cut]

Mask-6 is used for the formation of Contact -Cuts in S, D and G of n-MOS and p-MOS

[Step- Formation of Contact-Cut]

Mask-6 is used for the formation of Contact – Cuts in S, D and G of n-MOS and p-MOS

[Step- Formation of Contact-Cut]

Mask-6 is used for the formation of Contact – Cuts in S, D and G of n-MOS and p-MOS

[[Step- Metakkization]

[Step- Metakkization]

Mask-7 is used for the

deposition of metal in contact cuts

[Step- Metakkization]

Mask-7 is used for the deposition of metal in contact cuts

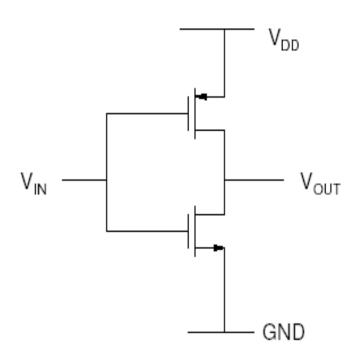

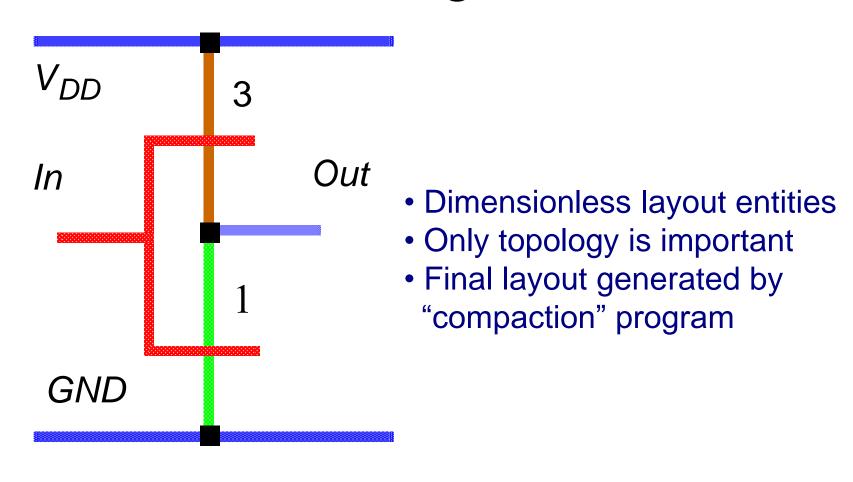

### Sticks Diagram

Stick diagram of inverter

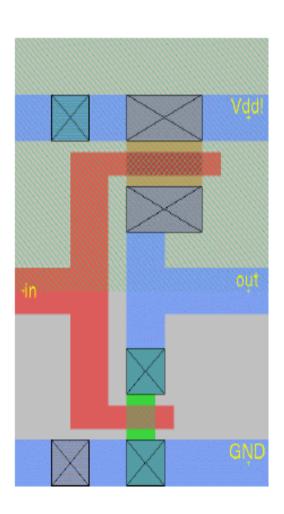

### Layout Design